The following ARM instruction can be used to return from an exception:

movs pc, lr

Apart from the program counter, which register is updated by this instruction?

Under which of the following circumstances is TLB maintenance always required?

An interrupt handler contains the following instruction sequence at the end. The purpose of these instructions is to clear the interrupt request in the interrupt controller and then safely re-enable interrupts.

STR r0, [r1] ; write to interrupt controller register to clear interrupt request

CPSIE i ; re-enable IRQ interrupts

Which of the following instructions should be placed at position

A Programmer's View CPU model usually provides:

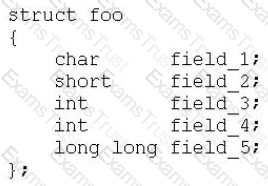

According to the EABI. what would the C size of () operator return when given the following structure?

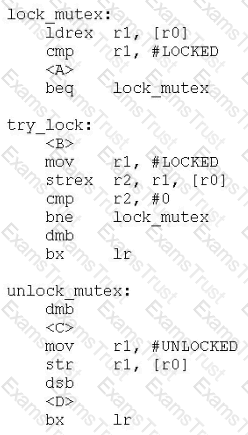

The following pair of functions implement a simple mutex spinlock which might be used to protect a critical code section in a multi-threaded application. The address of the lock variable is in r0.

In order to minimize power while waiting for the lock to be available. SEV and WFE instructions can be used to place the processor in a low power state while waiting for the lock to become available. At which points should these instructions be placed?

What is the value of R2 after execution of the following instruction sequence?

MOV R3, #0xBA

MOV R2/#0x10

BIC R2, R3, R2

An Advanced SIMD intrinsic has the prototype:

int16x4_t vmul_n_s16(int16x4_t a, int16_t b);

How many multiplications does this intrinsic compute?

Which of the following memory attributes, specified in a translation table entry, could be used to protect a page containing a read-sensitive peripheral from speculative instruction fetches?

Which of the following is an accurate description of network storage as compared to on-chip RAM?

Using a Generic Interrupt Controller (GIC), when the interrupt handler writes to the End of Interrupt Register (ICCEOIR), which of the following state transitions might occur for that interrupt ID?

What is an "Entry point" in an application?

In an MPCore system, when one core is waiting for resources to be released, what instruction could be used to reduce that core's power consumption?

What debugger view can you use to determine which function caused an exception?

Which TWO of the following accurately describe constraints on the location of the Tightly Coupled Memory (TCM) regions in a Cortex-R4 processor? (Choose two)

Which of the following features was added in version 2 of the ARM Architecture Advanced SIMD extensions?

The disassembly of a program written in C shows calls to the function__aeabi_fadd. Which one of these compiler floating point options could have been used?

Which privileged mode can kernel code use to get direct access to the User mode registers R13 and R14?

In a single-processor system, which of these operations requires a barrier instruction to guarantee correct operation?

Consider the following code sequence, executing on a processor which implements ARM Architecture v7-A.

LDR r0, [r1]

STR r0, [r2]

STR r3, [r3]

R1 points to a location in normal memory. R2 and R3 point to device memory.

Which of the following statements best describes the ordering rules which apply to this sequence?

Which power mode describes the state where the ARM processor is powered down, but its Level 1 caches remain powered?

In a symmetric multi-processing (SMP) software architecture, which of the following pairs of statements are TRUE? (Select the option in which BOTH statements are TRUE).

In an operating system environment, most applications are executed in which processor mode?

When linking with the standard C library, which library functions MUST be redefined in order to port your code to a new piece of production hardware?

Which of these instructions is a correct translation of the body of function f?

struct T { char a; int b; };

int f(struct T *p) { return p->b; }

The Q-flag in the program status register (PSR) indicates which of the following?

In Architecture ARMv7-A which one of the following has a known physical address at power-on reset?

Which of the following is a REQUIRED feature in the ARMv7 architecture?

Which of the following is an external exception?

In an ARMv7-A processor that includes the Advanced SIMD extension (NEON), where are the data values operated on by NEON instructions stored?

Within the ARMv7 architecture, which one of the following features is unique to the ARMv7-A profile?